CoWoP時代を見据えた半導体検査の今後の展望

プリント基板(PCB)とパッケージ基板を一体化することで、半導体パッケージの薄型化・広帯域化・熱性能の向上を実現するなど、次世代のシステムレベルパッケージングを可能にする技術として、CoWoP(Chip-on-Wafer-on-PCB)が注目を集めています。しかし、CoWoPに使用されるSLP(Substrate-Like PCB)を製造するには、半導体検査と同等の高度な外観検査(AOI)を行わなければなりません。以下では、ビジョン技術を活用し、CoWoPの実用化に向けたさまざまな検査課題を解決する方法について解説します。

CoWoPによるプリント基板とパッケージ基板の一体化

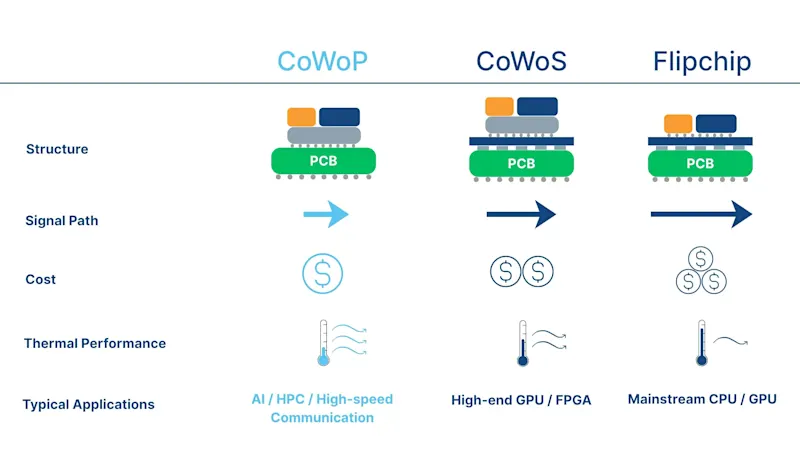

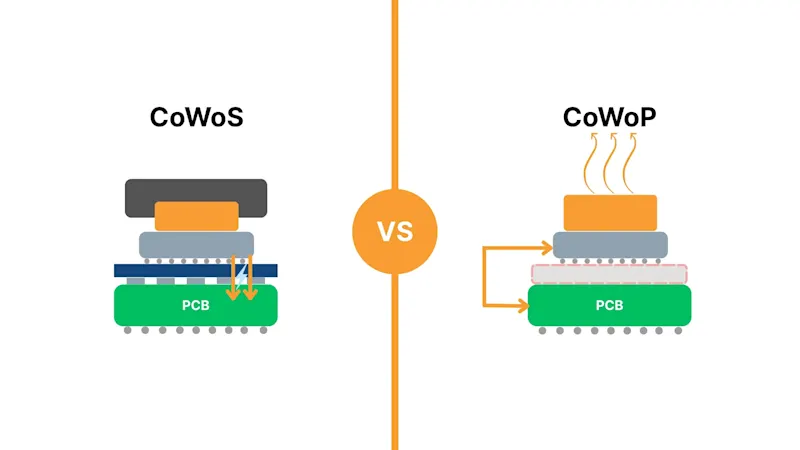

時代はCoWoSからCoWoPへ

CoWoS(Chip-on-Wafer-on-Substrate)技術が成熟し、NVIDIA社製H100、H200をはじめとするAI特化型の高性能GPUが登場するなか、業界の注目は次世代パッケージング技術のCoWoPへと向けられており、アドバンストパッケージング(先進パッケージング)を行う半導体メーカーと、大型基板を製造するプリント基板メーカーの境界線が再定義されようとしています。

TSMC社と大手半導体後工程(OSAT)企業の協力の下、NVIDIA社が開発を進めているCoWoPは、ABF(味の素ビルドアップフィルム)基板をはじめとする従来のパッケージ基板を排除し、シリコンインターポーザーと高密度プリント基板のSLPを直接接合することで、パッケージとシステムの一体化を可能にする技術です。

CoWoPの特長

技術的な観点から見た場合、CoWoPには、以下のような特長があります。

中継基板を排除し、信号経路を短縮することで、レイテンシーを抑えながら、電源品質を向上

ヒートスプレッダーを直接接続し、熱管理を改善

ABF/BT基板の代わりにSLPを使用し、パッケージングコストを40~50%削減

SLPは高速製造が可能であるため、検査・組立要件さえ満たせば、迅速な量産が可能

CoWoPにおけるSLPの重要性

CoWoPへの移行が進めば、プリント基板メーカーの重要性はますます高まるでしょう。

SLPに求められる役割は、電気的相互接続だけではありません。CoWoPパッケージの信号品質と電気性能を確保するには、HDI(高密度相互接続)やSAP(セミアディティブプロセス)法/MSAP(改良型セミアディティブプロセス)法により、積層数10層以上、L/S(線幅/線間隔)=15~20μmの高密度RDL(再配線層)を形成する必要があります。

しかも、広帯域幅・低レイテンシー・高い柔軟性を実現しながら、パッケージ基板のように反りや材料安定性にも配慮しなければなりません。このように、SLPはバリューチェーンの下流に位置する電子部品ではなく、半導体と同等の製品としてさまざまな課題に直面しているのです。

CoWoP向けSLP検査の精度要件と難易度

必要分解能15~20µmのCoWoP向けSLP検査は、必要分解能1~2µmの半導体パッケージング検査と比べると、精度要件こそ厳しくありませんが、その難易度は非常に高いといえます。

従来のパッケージ基板を排除し、SLPに直接チップを実装するCoWoP技術が普及すれば、さまざまな変化が起こるでしょう。SLPの加工技術と検査の安定性を含め、プリント基板メーカーにさらなる精度が求められるようになるほか、歩留まり管理についても、ビジョン技術を上手く活用し、単独検査から全層にわたる工程監視に移行する必要があります。

続きを読む

記事全文をご覧いただくには、以下のフォームへご入力ください。