CoWoP 崛起,半導體檢測全面到位

CoWoP 是一種新興的創新系統層級封裝技術,將封裝基板和 PCB 整合為單一結構,讓模組變得更薄、更高頻寛,且散熱性能更佳。為了達到這個目標,整個 PCB 供應鏈都必須達到半導體等級的精準度,因此先進的視覺檢測就變得非常重要。本文將探討半導體檢測技術如何適用於 CoWoP 製造,以及影響其成功的主要視覺檢測挑戰。

不只是電路板:CoWoP 將封裝層級的責任分配給 PCB

從 CoWoS 到 CoWoP

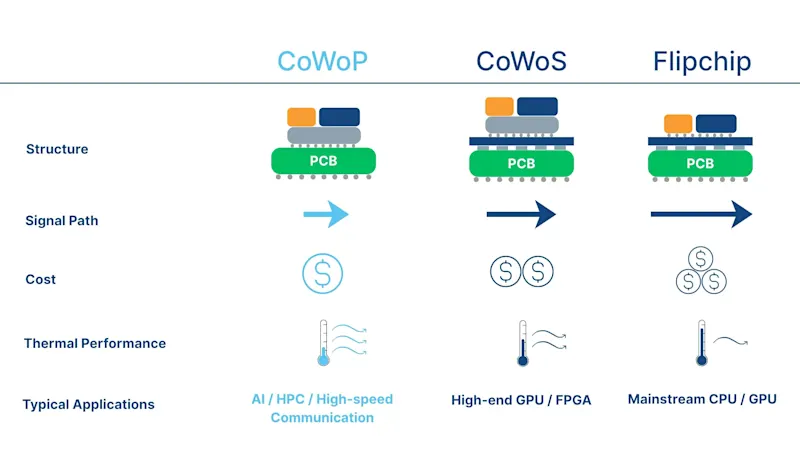

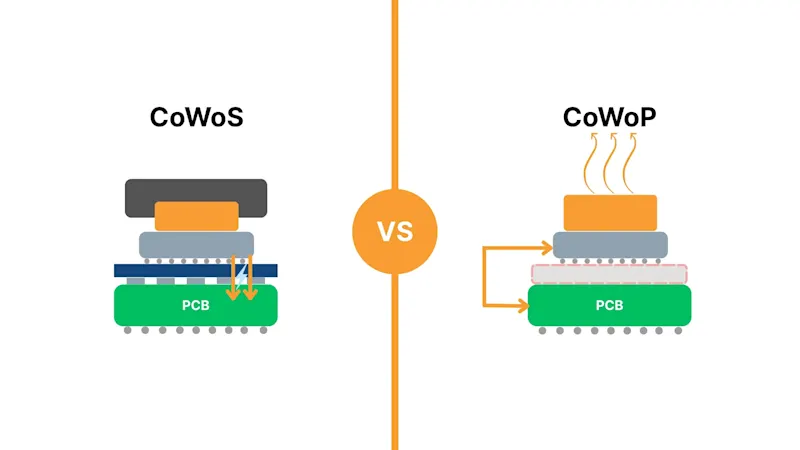

半導體與 PCB 產業再次重新定義其邊界。隨著 CoWoS (Chip-on-Wafer-on-Substrate) 技術日漸成熟,並且驅動今日的 AI 加速器 (例如 NVIDIA 的 H100 和 H200) ,業界的注意力正轉移至下一個重要概念 - CoWoP (Chip-on-Wafer-on-PCB) 。

CoWoP 由 NVIDIA 推廣,有台積電和主要 OSAT 的參與;這種技術移除傳統 ABF 基板,並直接將矽中介層接合至高精度 PCB 上,創造出結合先進封裝與大型面板製造的「封裝即系統」架構。

CoWoP 的優勢

從技術角度來看,CoWoP 有幾項明顯的優勢:

更短的訊號路徑省去了中間的基板,改善了資料延遲和電源完整性。

透過直接散熱器接觸來改善熱管理。

移除 ABF/BT 基板並使用大面積 PCB 製程,可將封裝成本降低 40-50%。

一旦檢驗和製程精確度達到基板等級,高產能 PCB 面板製造便可支援更快速的擴充能力。

CoWoP 需要類似基板的 PCB

然而,這種轉型也提升了 PCB 產業的角色。

在 CoWoP 架構中,PCB 不僅必須提供電氣互連,還必須透過 HDI 或 mSAP/SAP 製程形成精細的重布線層 (RDL),以確保訊號完整性和電源傳輸。

PCB 已不再是電子產品價值鏈的被動端,它現在面臨的是半導體等級的挑戰:要在 15-20 μm 的線寬/間距之間,建立多達 10 層以上的多層板、支援高頻寬、低延遲和設計彈性,同時還要維持與封裝基板相當的翹曲控制和材料穩定性。

如果 CoWoP 所需的精確度較低,為何會較難檢測?

乍看之下,CoWoP 15-20 µm 的檢測解析度,似乎不如半導體封裝的 1-2 µm 要求那麼高。然而其挑戰卻更大。

一旦移除基板,PCB 成為封裝,就改變了一切。CoWoP 將精準度的重擔轉移到下游:以往由基板製造端所處理的問題,現在取決於 PCB 製程及其檢測的穩定性。良率不再由單一步驟決定,而是由視覺系統在數十層積層中維持製程控制來決定。

繼續閱讀

填寫表單即可立即存取完整文章內容。