Real-Time Lead Frame Inspection: System Architecture Comparison of FPGA and CPU Processing

Lead frame defects can cause complete IC failure, resulting in costly production waste and returns. This article introduces a high-performance approach to inspection that shifts critical processing tasks—such as blob analysis and pixel-level parallelism—from CPU to FPGA. By addressing key limitations like excessive CPU usage, system instability, and programming complexity, Basler’s FPGA-based architecture empowers OEMs to build next-generation AOI systems capable of handling increasingly miniaturized lead frames with greater speed and reliability.

Capturing every detail in high-speed lead frame inspection

Lead frames are essential conductors between semiconductor chips and circuit boards. Even a single defect—such as edge burrs, corrosion, peeling or contamination—can result in electrical failure. For AOI system builders, ensuring accurate detection of both surface and dimensional defects across intricate lead patterns is critical, especially as inspection moves to higher speeds and finer tolerances.

Tackling the key challenges of lead frame inspection

Modern lead frame inspection demands a careful balance of precision, speed, and system stability.

On the imaging side, achieving consistent imaging contrast becomes more complex as lead frames shrink and materials become more reflective or varied. External factors like vibration and ambient light fluctuations further impact image reliability. These challenges can be mitigated using high-resolution cameras, carefully matched optics, and—in some cases—multi-spectral imaging. Our vision components are designed to integrate seamlessly into high-performance AOI platforms and support optimal imaging conditions.

On the processing side, inspection lines often need to exceed 100,000 units per hour, requiring real-time performance without compromising accuracy. At this scale, the architecture of the vision system—particularly how and where image data is processed—can either limit or unlock system-level performance.

In the next section, we compare CPU- and FPGA-based processing approaches to illustrate how FPGA architecture helps AOI system builders meet these demanding requirements.

Blob analysis at scale: FPGA’s architectural edge

To meet high throughput demands, blob analysis must handle thousands of lead frame “legs” per inspection frame with sub-micron precision. This process identifies connected pixel regions and extracts properties like size, contour, and position.

The challenge: CPU-based systems process data sequentially and are limited by software overhead, making large-scale blob analysis inefficient and less reliable.

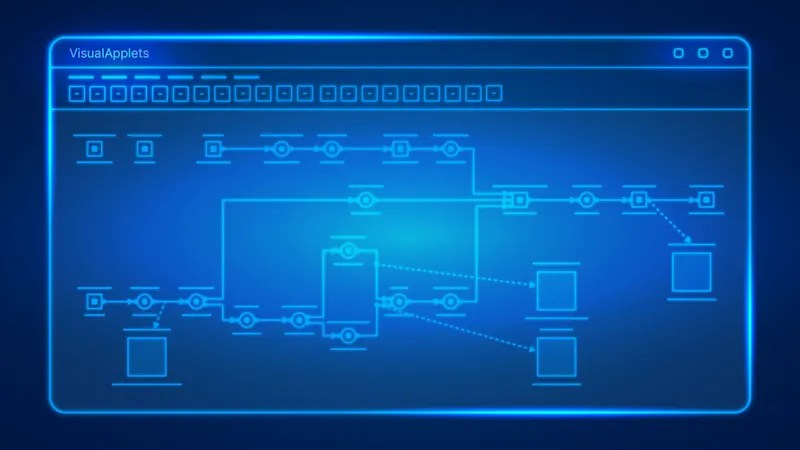

The solution: FPGA-based architecture enables true parallel pixel processing with sub-millisecond latency. Offloading blob analysis to the FPGA not only reduces CPU load but also boosts inspection reliability. While often associated with simple pre-processing, modern frame grabber FPGAs support advanced, high-speed logic. With VisualApplets, application engineers can implement and adapt FPGA-based processing flows without deep hardware coding—enabling faster development and easier updates.

Have a project? Let’s test it or talk it through.System architecture comparison: FPGA vs. CPU

Metric | FPGA-Based Systems | CPU-Based Systems |

|---|---|---|

Blob Processing | Parallel pixel pipelines (100+ ops/pixel) | Sequential thread-based analysis |

Latency | Sub-millisecond photon-to-decision | 10–100 ms (OS/software overhead) |

Power Efficiency | 3.5–5 W (optimized logic) | 15–30 W (general-purpose compute) |

Adaptability | Reconfigurable for new blob patterns/defects | Require software updates/retraining |

Lead frame inspection results: FPGA vs CPU-based systems

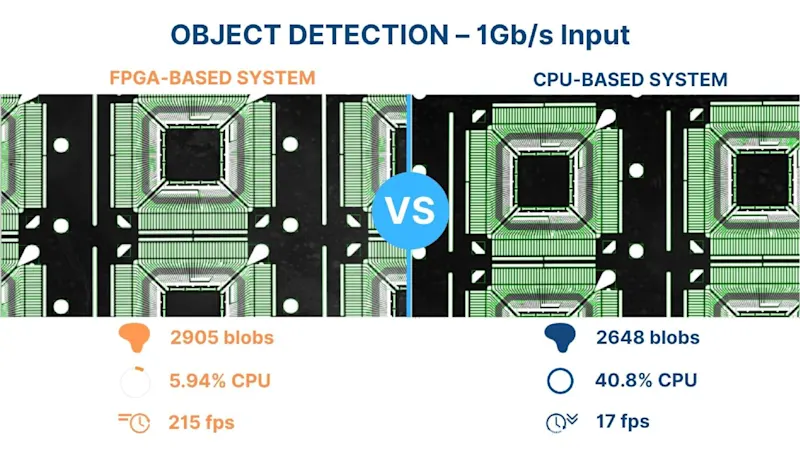

A demo was created to compare real-world performance between CPU- and FPGA-based vision processing systems. Setup details: identical 5MP CXP-12 camera running at 212 fps (~1 GB/s), identical PC environment, and the same lead frame object used for both systems.

FPGA-Based Systems | CPU-Based Systems * | |

|---|---|---|

Number of blobs detected | 2905 | 2648 |

Resolution | 5MP | 5MP |

Speed | Maintains 212 fps | 17 fps |

CPU Load | 5.94% | 40.8% |

* Note: Performance may vary based on software algorithm optimization. CPU based systems are more susceptible to frame drops, affecting blob count, image overlays, and defect classification.

Conclusion: FPGA-based image pre-processing streamlines machine vision data at the source

FPGA-based vision architecture offers clear advantages for high-throughput, high-precision lead frame inspection. By processing image data directly in hardware, they significantly reduce CPU dependency, improve throughput, and enhance system stability. For AOI system builders, this not only boosts performance but also creates a more scalable and maintainable platform.

With VisualApplets, complex FPGA logic can be implemented and iterated quickly—without traditional HDL programming—enabling fast adaptation to evolving inspection requirements. In today’s increasingly demanding packaging environments, FPGA is not just an upgrade—it's a strategic architectural shift.

Products for this solution

Looking to implement a comparable solution? These products will help you.