導線架即時檢測:FPGA 與 CPU 處理的系統架構比較

導線架的缺陷可能導致 IC 完全失效,造成高成本的生產浪費和退貨。本文將介紹一種高效能的檢測方法,該方法可將關鍵的處理任務 (例如 blob 分析和畫素層級的平行處理) 從 CPU 轉移到 FPGA。Basler 以 FPGA 為基礎的架構解決了 CPU 使用率過高、系統不穩定性和程式複雜性等關鍵限制,使 OEM 能夠建立下一代 AOI 系統,以更快的速度和更高的可靠性,對日益微型化的導線架進行處理。

以高速進行導線架檢測時拍下所有細節

導線架是介於半導體晶片與電路板之間的重要導體。即使是一個小缺陷,例如邊緣毛刺、腐蝕、剝落或污染,都可能導致電氣故障。對於 AOI 系統製造商而言,確保精確偵測複雜導線樣式的表面與尺寸缺陷至關重要,尤其是當檢測速度更快、公差更細時。

解決導線架檢驗的主要挑戰

當代導線架檢測作業需要小心平衡精確度、速度和系統穩定性。

在影像方面,由於導線架縮小、材料變得更具反射性,或形式變化更多,要達到一致的影像對比變得更加複雜。振動和環境光波動等外部因素,也會進一步影響影像的可靠性。這些挑戰可以使用高解析度相機,精心挑選的光學元件,以及在某些情形下使用多頻段成像技術。我們的視覺元件可完美整合至高效能的 AOI 平台,並支援最佳的成像條件。

在處理方面,檢測線通常需要處理每小時 100,000 單元以上,因此需要即時效能,同時又不影響精確度。在這種規模下,視覺系統的架構 (尤其是影像資料的處理方式與位置) 往往對系統層級效能具有正面或負面的影響。

在下一節中,我們會比較 CPU 和 FPGA 的處理方法,以說明FPGA 架構如何 協助 AOI 系統製造商滿足這些嚴苛的要求。

大規模 Blob 分析:FPGA 的架構優勢

為了滿足高通量需求,blob 分析必須以次微米精度,處理每個檢測框中數以千計的導線框引腳。此流程可辨識連接的畫素區域,並拍攝尺寸、輪廓和位置等屬性。

挑戰: 以 CPU 為基礎的系統依序處理資料,並受到軟體操作負荷的限制,在進行大規模 blob 分析時效率低、可靠性也不佳。

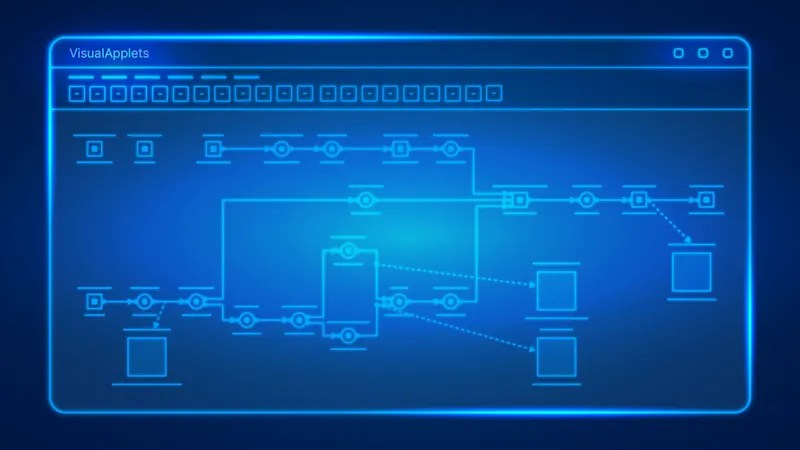

解決方案: 以 FPGA 為基礎的架構,能夠以毫秒以下的延遲,進行真正的平行畫素處理。將 blob 分析卸載至 FPGA,不僅可降低 CPU 負載,還能提升檢測可靠性。現代的影像擷取 FPGA 支援先進的高速邏輯,通常會用以進行簡單的預處理。使用VisualApplets, 應用工程師能夠執行並適配FPGA 處理無需深入硬體程式撰寫流程,加快開發速度更快並簡化更新。

有專案嗎?讓我們一起測試、討論。系統架構比較:FPGA vs. CPU

指標 | FPGA 系統 | CPU 系統 |

|---|---|---|

Blob 處理 | 平行畫素管線 (100+ ops/pixel) | 循序執行序分析 |

延遲 | 一毫秒以下光子到決策 | 10-100 ms (OS/ 軟體操作負荷) |

電源效率 | 3.5-5 W (最佳化邏輯) | 15-30 W (一般用途運算) |

適配能力 | 可針對新的 blob 圖案/瑕疵進行重新配置 | 需要軟體更新/再訓練 |

導線架檢測結果:FPGA vs CPU 系統

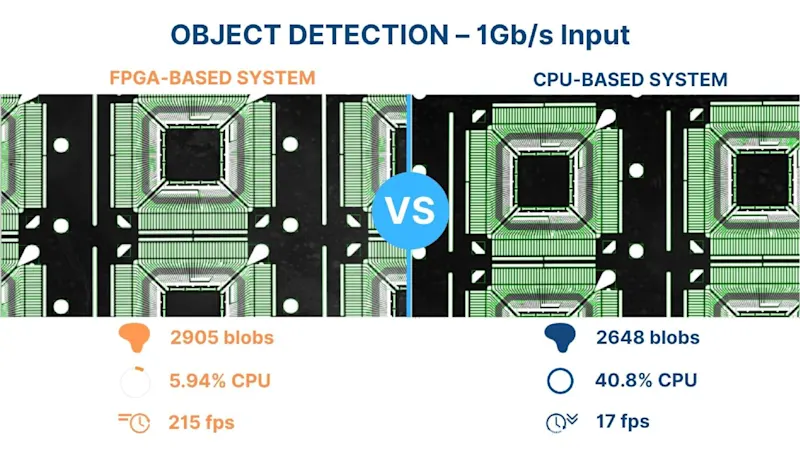

我們製作了一個示範,來比較 CPU 和 FPGA 視覺處理系統的實際效能。 設定細節 相同的 5MP CXP-12 相機、 執行速度為 212 fps (~1 GB/s)、相同的 PC 環境、兩個系統使用相同的導線架主體。

FPGA 系統 | CPU 系統 * | |

|---|---|---|

偵測到的 Blobs 數量 | 2905 | 2648 |

解析度 | 5MP | 5MP |

速度 | 維持 212 fps | 17 fps |

CPU 負載 | 5.94% | 40.8% |

* 註:效能可能因軟體演算法最佳化而異。以 CPU 為基礎的系統較容易發生影格流失,影響 Blob 計數、影像重疊和瑕疵分類。

結論:以 FPGA 為基礎的影像預處理,可在源頭簡化機器視覺資料

FPGA 視覺架構為高產量、高精度導線架檢測帶來明顯的優勢。直接以硬體處理影像資料,可大幅降低對 CPU 的依賴、提高產量,並加強系統穩定性。對於 AOI 系統建置商而言,不僅能夠提升效能,還能建立更具擴充性與可維護性的平台。

有了 VisualApplets,複雜的 FPGA 邏輯可以快速實作迭代,無需使用傳統 HDL 程式設計,因此能夠快速適應不斷演進的檢測需求。在現今要求日益嚴苛的封裝環境中,FPGA 不只是一種升級,更是一種策略性的架構轉換。

此方案所用產品

想實施類似的方案嗎?這些產品能有所助益。