CoWoP Is Coming, and Semiconductor Inspection Is Ready All Along

CoWoP, the emerging system-level packaging innovation, integrates the package substrate and PCB into a single structure, enabling thinner, higher-bandwidth modules with improved thermal performance. To achieve this, the entire PCB supply chain must reach semiconductor-grade accuracy, making advanced vision inspection essential. This article explores how semiconductor inspection technologies can be adapted for CoWoP manufacturing and the key vision inspection challenges shaping its success.

More than a circuit board: CoWoP assigns packaging-level responsibilities to PCB

From CoWoS to CoWoP

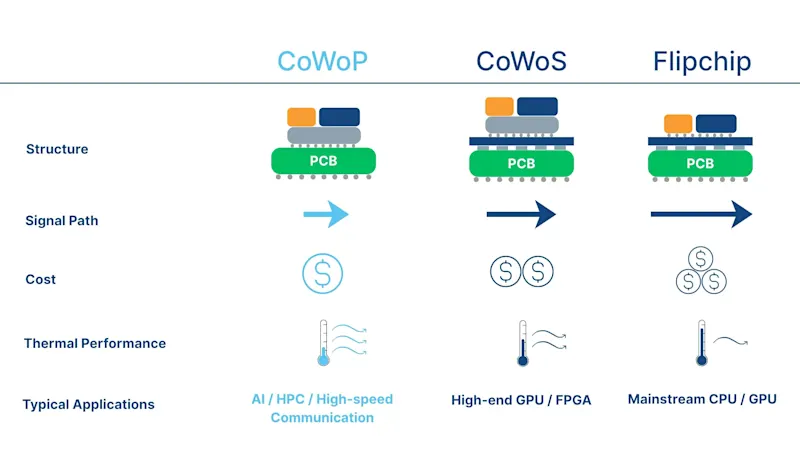

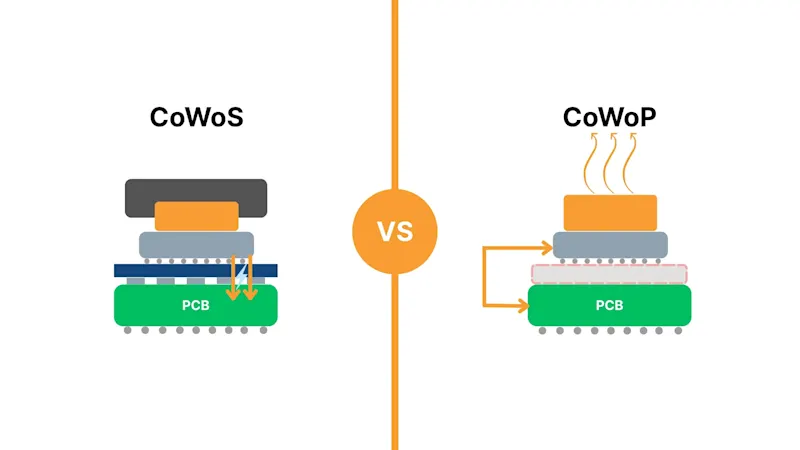

The semiconductor and PCB industries are once again redefining their boundaries. As CoWoS (Chip-on-Wafer-on-Substrate) technology matures and powers today’s AI accelerators such as NVIDIA’s H100 and H200, industry attention is shifting to the next major concept — CoWoP (Chip-on-Wafer-on-PCB).

Driven by NVIDIA, with participation from TSMC and major OSATs, CoWoP removes the traditional ABF substrate and directly bonds the silicon interposer to a high-precision PCB, creating a “package-as-system” architecture that merges advanced packaging and large-panel manufacturing.

CoWoP advantages

From a technical standpoint, CoWoP offers several clear advantages:

Shorter signal paths improve data latency and power integrity by eliminating the intermediate substrate.

Improved thermal mangement via direct heat-spreader contact.

The removal of ABF/BT substrates and use of large-panel PCB processes can cut packaging costs by 40–50%.

High-throughput PCB panel manufacturing supports faster scaling once inspection and process precision reach substrate levels.

CoWoP demands substrate-like PCB

Yet this transition also elevates the role of the PCB industry.

In the CoWoP architecture, the PCB must not only provide electrical interconnection but also form fine redistribution layers (RDLs) through HDI or mSAP/SAP processes to ensure signal integrity and power delivery.

No longer the passive end of the electronics value chain, the PCB now faces semiconductor-level challenges: building up to 10+ multilayers with 15–20 μm line/space, supporting high bandwidth, low latency, and design flexibility, while maintaining warpage control and material stability comparable to packaging substrates.

If CoWoP needs less precision, why is it harder to inspect?

At first glance, CoWoP’s inspection resolution of 15–20 µm seems less demanding than semiconductor packaging’s < 1–2 µm range. Yet the challenge is greater.

Once you remove the substrate, the PCB becomes the package, and that changes everything. CoWoP shifts the precision burden downstream: what used to be handled by substrate manufacturing now depends on PCB processes and their inspection stability. Yield is no longer defined by one step, but by how well vision systems can maintain process control across dozens of buildup layers.

Continue Reading

Complete the form to access the full article instantly.